条件:输入85-265V交流,整流后直流100-375V输出12V/5A

初级电感量370uH初级匝数:40T,次级:5T

次级滤波电容1000uFX3=3000uF震荡三角波幅度.2.5V开关频率100K

电流型控制时,取样电阻取0.33欧姆

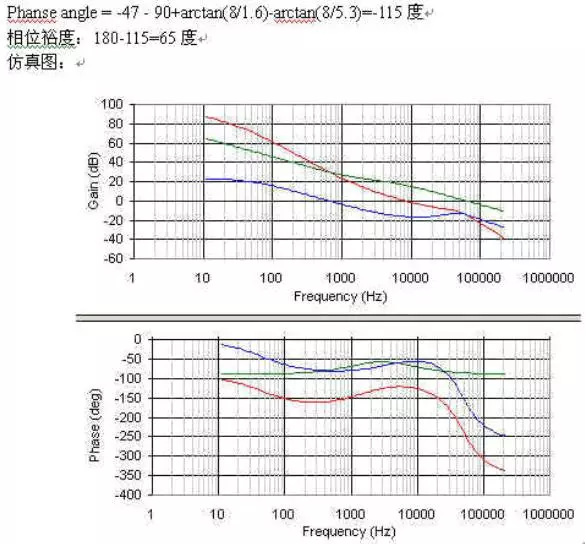

下面分电压型和峰值电流型控制来设计此电源环路.所有设计取样点在输出小LC前面.如果取样点在小LC后面,由于受LC谐振频率限制,带宽不能很高.1)电流型控制

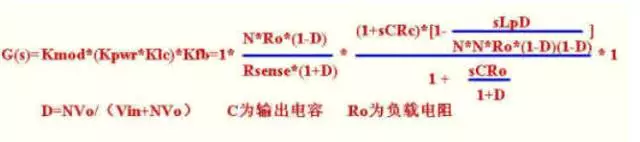

假设用3842,传递函数如下

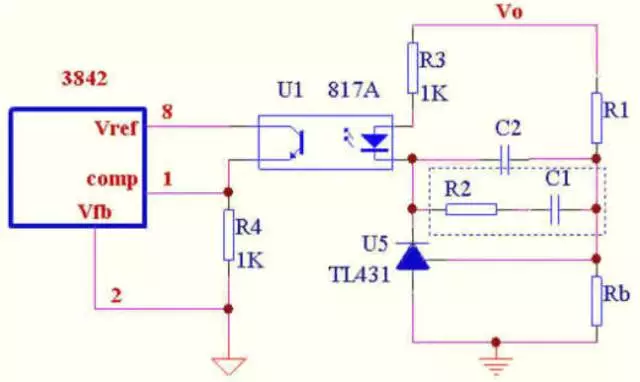

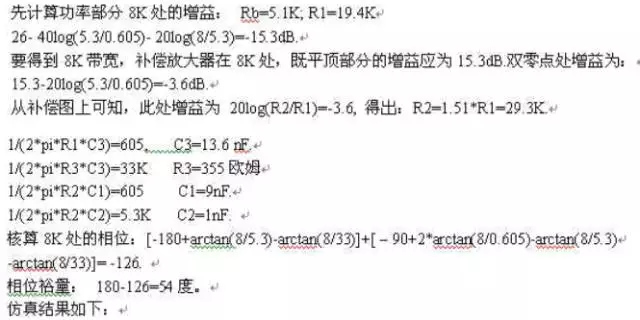

此图为补偿放大部分原理图.RHZ的频率为33K,为了避免其引起过多的相移,一般取带宽为其频率的1/4-1/5,我们取1/4为8K.

分两种情况:

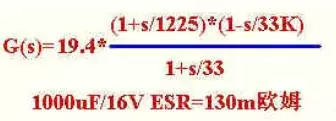

A)输出电容ESR较大

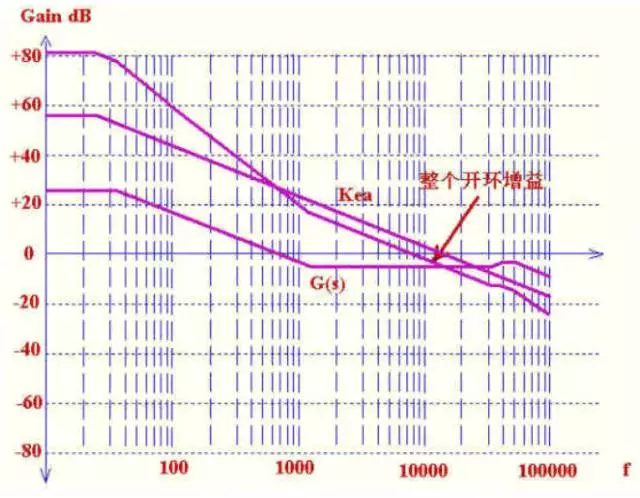

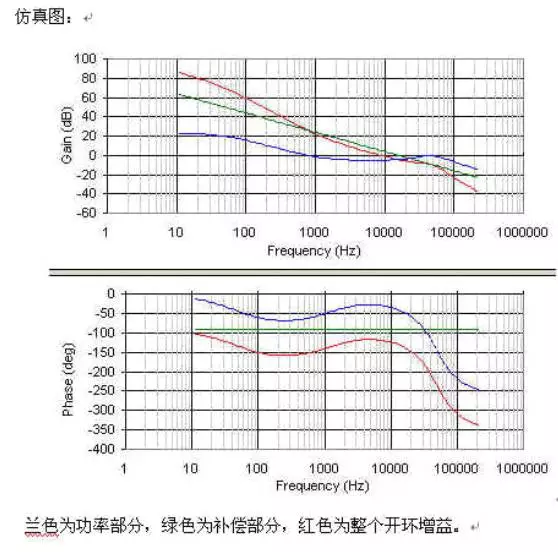

输出滤波电容的内阻比较大,自身阻容形成的零点比较低,这样在8K处的相位滞后比较小.Phanseangle=arctan(8/1.225)-arctan(8/0.033)-arctan(8/33)=--22度.

另外可看到在8K处增益曲线为水平,所以可以直接用单极点补偿,这样可满足-20dB/decade的曲线形状.省掉补偿部分的R2,C1.

设Rb为5.1K,则R1=[(12-2.5)/2.5]*Rb=19.4K.

8K处功率部分的增益为-20*log(1225/33)+20*log19.4=-5.7dB因为带宽8K,即8K处0dB

所以8K处补偿放大器增益应为5.7dB,5.7-20*log(Fo/8)=0Fo为补偿放大器0dB增益频率Fo=1/(2*pi*R1C2)=15.42

C2=1/(2*pi*R1*15.42)=1/(2*3.14*19.4*15.42)=0.53nF相位裕度:180-22-90=68度

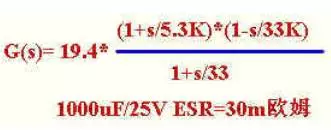

输出滤波电容的内阻比较大,自身阻容形成的零点比较高,这样在8K处的相位滞后比较大.

Phanseangle=arctan(8/5.3)-arctan(8/0.033)-arctan(8/33)=-47度.

如果还用单极点补偿,则带宽处相位裕量为180-90-47=43度.偏小.用2型补偿来提升.

三个点的选取,第一个极点在原点,第一的零点一般取在带宽的1/5左右,这样在带宽处提升相位78度左右,此零点越低,相位提升越明显,但太低了就降低了低频增益,使输出调整率降低,此处我们取1.6K.第二个极点的选取一般是用来抵消ESR零点或RHZ零点引起的增益升高,保证增益裕度.我们用它来抵消ESR零点,使带宽处保持-20db/10decade的形状,我们取ESR零点频率5.3K

数值计算:

8K处功率部分的增益为-20*log(5300/33)+20*log19.4=-18dB

因为带宽8K,即最后合成增益曲线8K处0dB

所以8K处补偿放大器增益应为18dB,5.3K处增益=18+20log(8/5.3)=21.6dB水平部分增益=20logR2/R1=21.6

推出R2=12*R1=233Kfp2=1/2*pi*R2C2

推出C2=1/(2*3.14*233K*5.4K)=127pF.fz1=1/2*pi*R2C1

推出C1=1/(2*3.14*233K*1.6K)=0.427nF.

相位

fo为LC谐振频率,注意Q值并不是用的计算值,而是经验值,因为计算的Q无法考虑LC串联回路的损耗(相当于电阻),包括电容ESR,二极管等效内阻,漏感和绕组电阻及趋附效应等.在实际电路中Q值几乎不可能大于4—5.

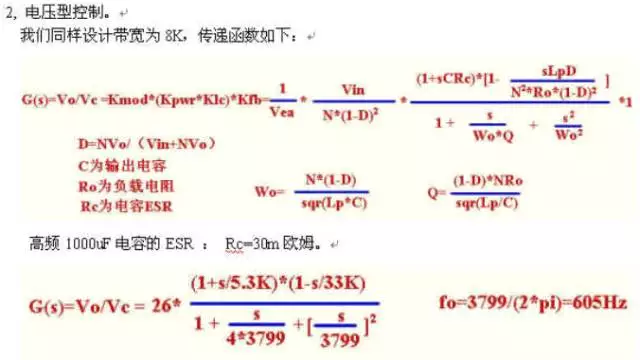

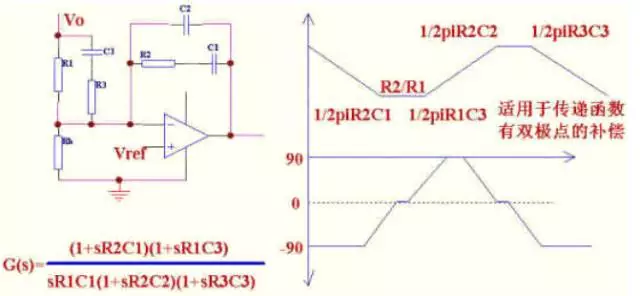

由于输出有LC谐振,在谐振点相位变动很剧烈,会很快接近180度,所以需要用3型补偿放大器来提升相位.其零,极点放置原则是这样的,在原点有一极点来提升低频增益,在双极点处放置两个零点,这样在谐振点的相位为-90+(-90)+45+45=-90.在输出电容的ESR处放一极点,来抵消ESR的影响,在RHZ处放一极点来抵消RHZ引起的高频增益上升.

元件数值计算,为方便我们把3型补偿的图在重画一下.

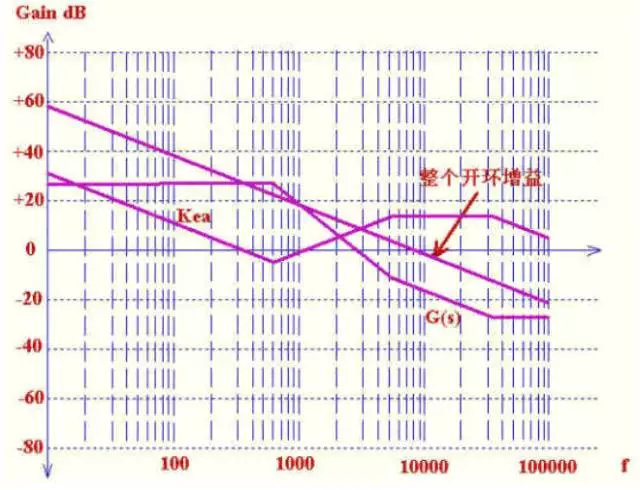

兰色为功率部分,绿色为补偿部分,红色为整个开环增益.

如果相位裕量不够时,可适当把两个零点位置提前,也可把第一可极点位置放后一点.

同样假设光耦CTR=1,如果用CTR大的光耦,或加有其他放大时,如同时用IC的内部运放,只需要在波得图上加一个直流增益后,再设计补偿部分即可.这时要求把IC内部运放配置为比例放大器,如果再在内部运放加补偿,就稍微麻烦一点,在图上再加一条补偿线结束.

我想大家看完后即使不会计算,出问题时也应该知道改哪里.